YoheiNishino - 19:31, Thursday 19 September 2024 (3746)

Frequency response of PFD circuit

Nishino

This is a continous work of 3707.

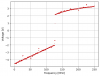

I measured frequency response of the PFD circuit (in 3707 we reported phase response). Input volatages are 1 Vpp for both two inputs. LO is fixed to 125 MHz sine wave, while RF side is scanned from 1 MHz to 250 MHz.

As shown in Fig.2, the output signal (=error signal) crosses zero when RF frequency matches with LO frequency. It is confirmed that this circuit can be used for PLL.

Images attached to this report